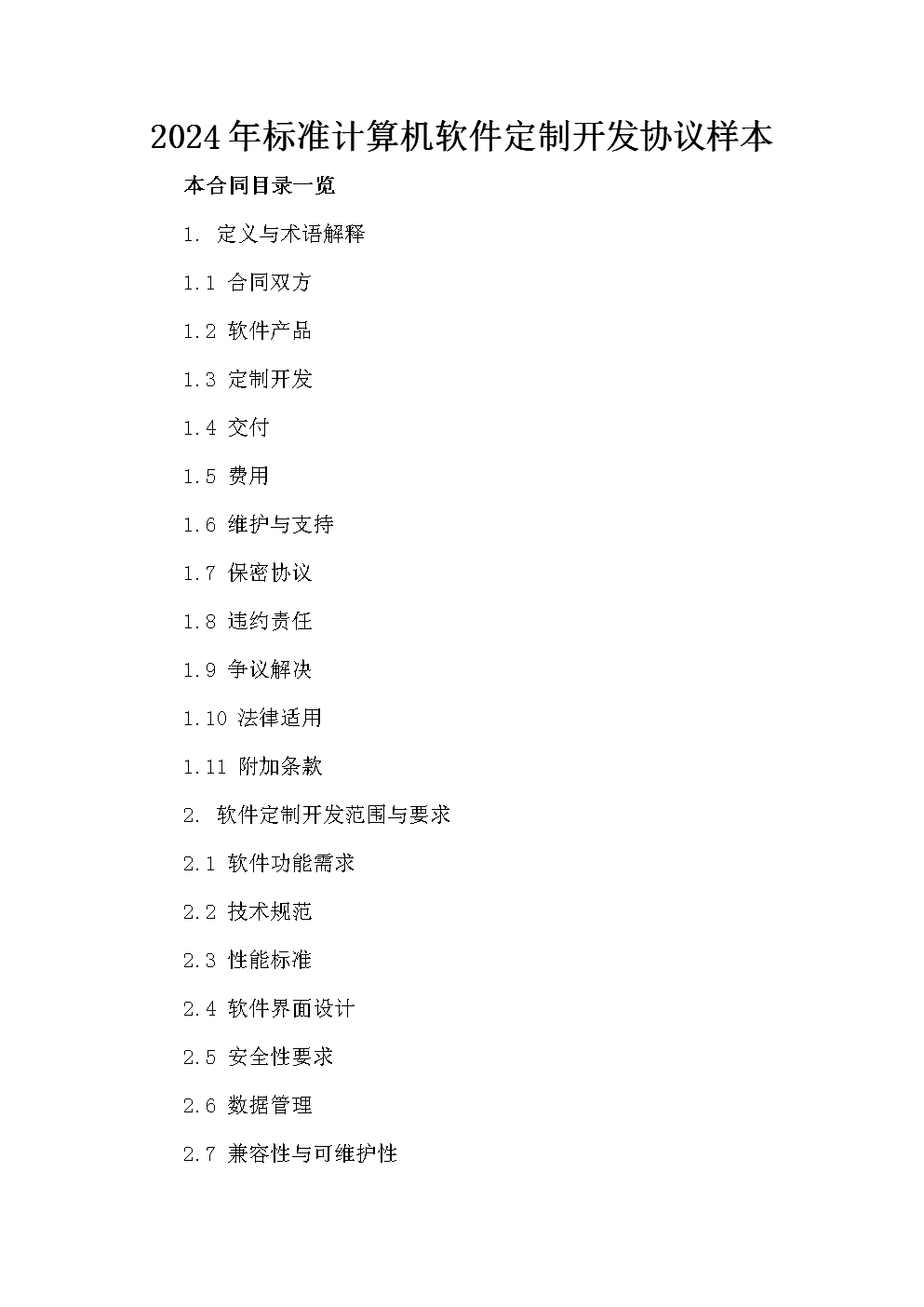

《計算機(jī)組成與設(shè)計:硬件/軟件接口》第三版是計算機(jī)科學(xué)領(lǐng)域的經(jīng)典教材,深入探討了計算機(jī)硬件與軟件的交互原理。本文結(jié)合教材內(nèi)容,針對電腦軟件設(shè)計與開發(fā)實踐,提供關(guān)鍵知識點解析與學(xué)習(xí)指導(dǎo)。

一、硬件與軟件接口的核心概念

教材強(qiáng)調(diào)從底層硬件到高級軟件的完整視角,重點包括:指令集架構(gòu)(如MIPS)、處理器數(shù)據(jù)通路設(shè)計、存儲器層次結(jié)構(gòu)以及I/O系統(tǒng)。理解這些硬件基礎(chǔ)是高效軟件開發(fā)的先決條件,例如,緩存一致性機(jī)制直接影響多線程程序的性能優(yōu)化。

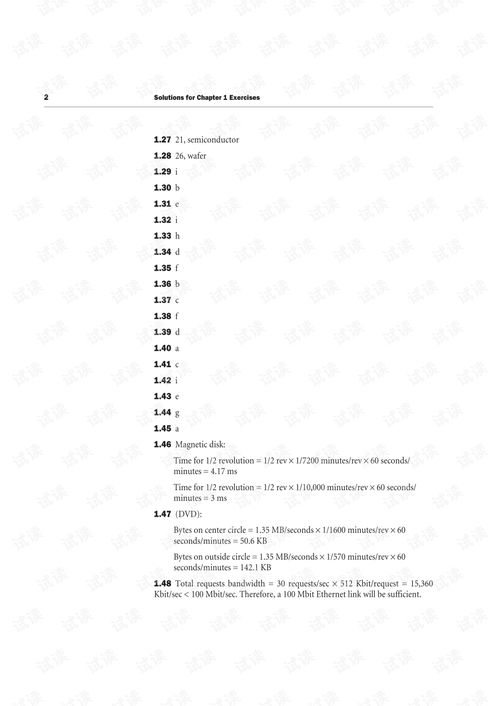

二、實踐答案與開發(fā)應(yīng)用

對于課后習(xí)題與項目實踐,答案需體現(xiàn)硬件約束下的軟件設(shè)計思維:

- 性能分析:通過計算CPI(每條指令周期數(shù))和Amdahl定律,評估代碼在特定硬件上的效率。

- 并行編程:基于多核處理器特性,設(shè)計線程同步方案,避免資源競爭導(dǎo)致的死鎖。

- 編譯器優(yōu)化:利用指令級并行性(如流水線技術(shù))調(diào)整代碼結(jié)構(gòu),減少流水線停頓。

三、軟件開發(fā)中的硬件意識

現(xiàn)代軟件設(shè)計必須兼顧硬件特性:

- 內(nèi)存管理:理解虛擬內(nèi)存與TLB(轉(zhuǎn)址旁路緩存)機(jī)制,可減少頁面錯誤,提升應(yīng)用響應(yīng)速度。

- 能效設(shè)計:針對移動設(shè)備,采用動態(tài)電壓頻率調(diào)整(DVFS)算法,平衡計算性能與功耗。

- 安全考量:硬件輔助的地址空間隨機(jī)化(ASLR)為軟件提供底層防護(hù),防止緩沖區(qū)溢出攻擊。

四、案例:嵌入式系統(tǒng)開發(fā)

以物聯(lián)網(wǎng)設(shè)備為例,硬件資源受限(如有限緩存與低功耗CPU),軟件需精簡指令集、采用實時操作系統(tǒng)(RTOS),并通過硬件抽象層(HAL)實現(xiàn)跨平臺兼容。教材中的中斷處理與DMA(直接內(nèi)存訪問)章節(jié)為此提供理論支撐。

掌握硬件/軟件接口知識,不僅能解析教材習(xí)題,更能指導(dǎo)實際軟件開發(fā),構(gòu)建高效、可靠的計算機(jī)系統(tǒng)。建議結(jié)合模擬器(如Gem5)與原型開發(fā)板,將理論答案轉(zhuǎn)化為實踐成果。